新手的Vivado Block Design踩坑小记

最近在使用Vivado的Block Design搭建SoC,由于许多东西的User Guide不知道去哪找,因此在这里整理了一下自己作为新手使用Block Design踩过的坑。

1. 需要Create HDL Wrapper

在BD搭建完成后,点击右键选Create HDL Wrapper,然后就可以作为Top或是在别的模块中例化了。

2. 无法将System Verilog作为模块

遇到一个大问题就是自己写的System Verilog模块怎么都无法加入。后来查阅UG994发现直到Vivado 2021.2依然不支持将System Verilog作为Block Design的顶层模块。当然解决方法也非常简单,写一个Verilog作为wrapper即可。

3. 自动识别AXI等接口的信号

相信许多人选择Block Design的原因就是AXI连接非常方便。显然在BD中继续一条一条线接AXI是不合适的。这个问题同样在UG994中提及,搜索"Inferring AXI Interfaces"即可。

顺便,自己写了一个能够使AXI命名符合Vivado要求的wrapper生成器,位于github.com/cyyself/axi-signal-wrapper 。能够支持Rocket Chip与Chipyard。

4. 自动识别了错误的时钟导致时钟报错

如果仅仅是频率不对,可以在时钟信号上双击,可以修改。

如果自动识别到非同一个时钟域,但其实连接的时钟等价,这时候可以自己写一个wrapper去掉某一个或多个时钟即可。

5. MIG稍微动动就损坏

可以对.bd点击右键,选择Reset Output Products重新生成MIG。

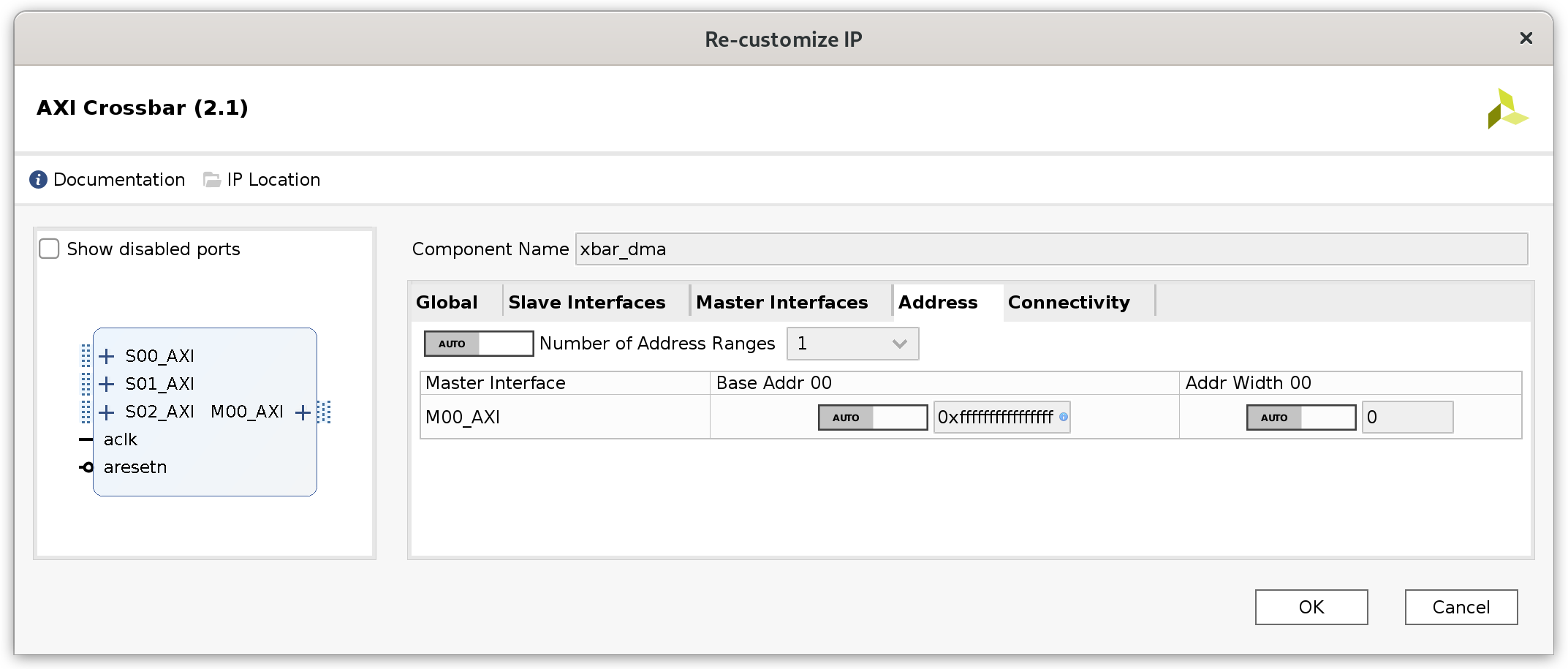

6. AXI Crossbar自动生成的Address出现base address全1而width全0。

发生在AXI DMA接AXI Crossbar时,由于只有一个AXI Master接口,因此没有出现在Address Map中,结果AXI Crossbar自动生成的地址出现为base address全1,而width全0,进而导致AXI DMA无法工作。手动修改base address为0,width为axi接口宽度后恢复正常。