背景 最近朋友 Easton Man 告诉了我一些SPEC CPU 2006 与 2017 的一些性能计数器 Topdown 统计结果,在观测他的结果后我惊讶地发现,SPEC CPU 2017中 mcf 这一 workload 对…

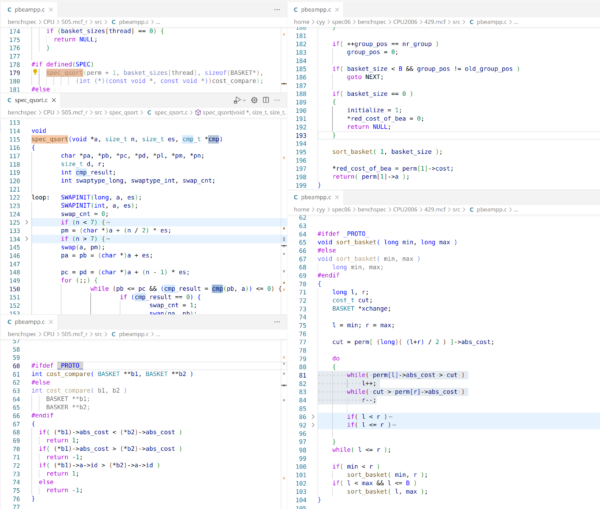

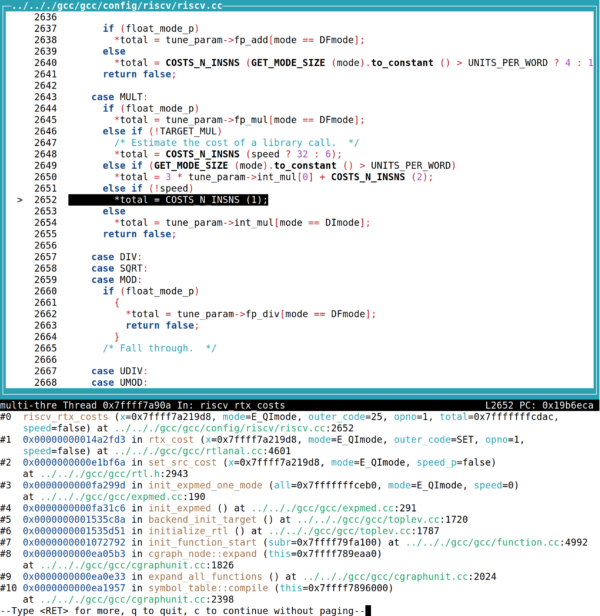

从CPU RTL到GCC expmed Cost Model

背景 最近和朋友讨论一个编码算法的问题的时候意外发现,当前 RISC-V 的 GCC 即使使用-O3优化的情况下,也不会将 divide by const 优化为Barrett reduction。但我测试了默认参数的 x86 、 aarch64 、 mips32 ,均存在该优化。且通常来说, CPU…

修好了D1板板使用Clang编译内核的问题,错误的Variables in Specified Registers用法

最近在修D1板板的驱动。遇到一些很迷惑的问题。 GCC编译的D1内核是好的,Clang不开LTO的内核是坏的,Clang编译的LTO THIN的内核是坏的,Clang编译的LTO Full内核勉强能用,Clang编译的LTO Full+CFI的内核是坏的。 但由于我们科研需要必须要使用Clang LTO+CFI,因此必须要保证能跑通开启了LTO和CFI的Kernel。 上述勉强能用的内核网卡还出现了异常的延迟、丢包、DUP。且从板子上ping外部延迟恒定为1s,而从外部ping板子延迟恒定为2s。而IPv6甚至完全不可用。 而勉强能用的内核上的SD卡,挂载上去写完文件再卸载后,接到别的电脑上挂载,却出现了文件系统损坏的情况。 而后来,经过2老师测试勉强能用的内核上的网卡驱动,发现以下问题: 经研究,clang编译的d1 linux,发包时,如果同时收到了包(比如别人发的广播包),那么发出去的包部分字节会被覆盖为收到的包 因此,我开始怀疑该问题是访问IO时Cache一致性出了问题,我就把目光从驱动本身转向了内核里维护Cache一致性的相关代码。 后来,我发现了一个这样的函数: void sbi_dma_sync(unsigned long start,…

AMD Zen 2/3处理器上的迷惑现象

今天在实验室装了一台AMD Ryzen 5700G的机器,想看看和自己寝室里放的AMD Ryzen 5800X性能差距多少,考虑到架构相同仅L3 Cache大小不同,因此就进行了一个简单的循环测试来看看单核Turbo Boost性能差距有多大。 实验室的5700G机器上安装了Ubuntu 21.04(考虑到20.04目前内核版本为5.4,无法支持Zen 3的一些电源管理特性,而实验室同学喜欢用Ubuntu),而我自己台式机则是滚的Debian sid。 两台机器自带的编译器如下(后续已经发现只与编译器有关): 实验室的5700G:gcc version 10.3.0 (Ubuntu 10.3.0-1ubuntu1) 寝室的5800X:gcc…

修改binutils在RISC-V上添加汇编指令

1. 起源 最近给学长打工做的相关研究需要对RISC-V指令集进行扩展,因此需要魔改编译器添加指令。 而RISC-V架构上做到这一点其实非常容易,官方提供了一个riscv-opcodes工具,它可以用于生成编译器所需的opcode宏来添加所需的指令。 2. 准备环境 我的实验基于Debian Bullseye发行版进行。(写这篇文章之时Bullseye还处于Testing状态) 首先我们需要编译安装riscv-gnu-toolchain. sudo apt-get install autoconf automake autotools-dev curl python3 libmpc-dev…